在微控制器领域,Fremont Micro Devices 的 FT60F010A-URT 是一款备受关注的芯片。它以其高性能、低功耗和丰富的功能集,广泛应用于各种嵌入式系统。本文将深入探讨 FT60F010A-URT 的数字功能框图、程序存储器布局以及脚位图,帮助开发者更好地理解和应用这款芯片。

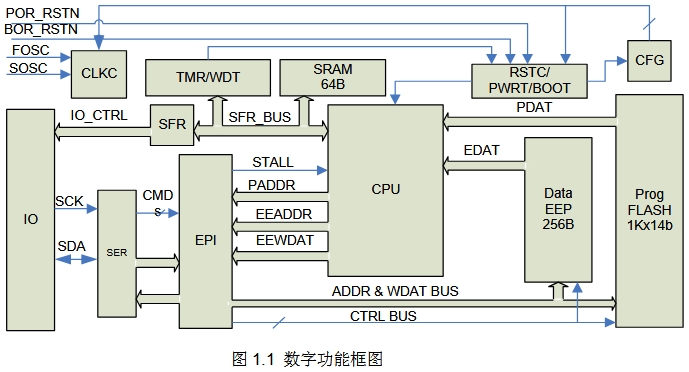

FT60F010A-URT 的数字功能框图是理解其内部架构和工作原理的关键。该芯片集成了多个功能模块,包括定时器、看门狗定时器、数据 EEPROM、I/O 端口等。以下是其数字功能框图的主要组成部分及其功能描述:

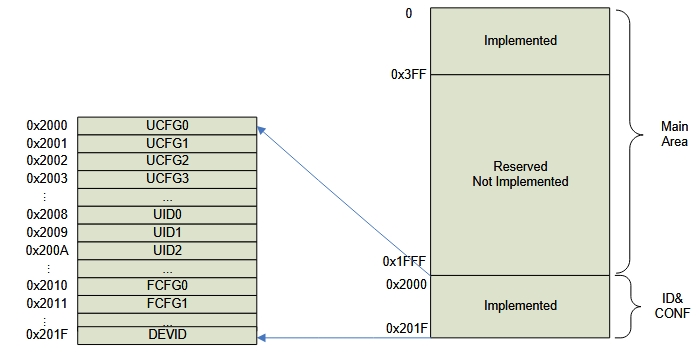

FT60F010A-URT 的程序存储器布局如下表所示:

| 地址范围 | 描述 |

|---|---|

| 0x0000 - 0x03FF | 主程序存储区 |

| 0x2000 - 0x201F | 配置信息和 ID 存储区 |

地址寄存器为 13 位 (0x0000 ~ 0x1FFF),最多支持 8K 地址空间。程序存储器一共 1Kx14b (0x0000 ~

0x03FF),加上额外 ID 和配置信息区,共 32x14b,它们由 FLASH 构成。一个 PAGE 是 16 个字,一共有 66个 PAGE。

其中 0~0x03FF 对主程序区访问,其中未实现部分 0x400~0x1FFF 保留。ID 和配置信息区从 0x2000 开始,到 0x201F 结束。

主程序存储区的地址范围为 0x0000 到 0x03FF,总共 1Kx14b 的存储空间。程序存储器被划分为 66 个页面,每个页面包含 16 个字。这种分页存储方式便于程序的组织和管理,同时也支持高效的程序执行。

配置信息和 ID 存储区位于 0x2000 到 0x201F,用于存储芯片的配置参数和唯一标识符。这些信息在芯片初始化时被加载,用于配置芯片的工作模式和参数。

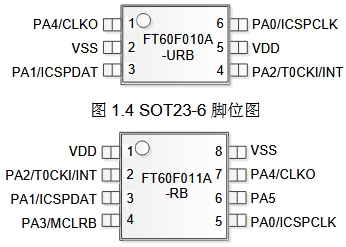

FT60F010A-URT 提供了两种封装方式:SOT23-6 和 SOP-8。以下是这两种封装方式的脚位图及其详细描述:

| 管脚名 | 功能名 | 输入信号类型 | 输出信号类型 | 具体描述 | 上下拉 |

|---|---|---|---|---|---|

| PA0/ICSPCLK | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Debug/烧录模式串口clock信号 | 可配置上拉 |

| PA1/ICSPDAT | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Debug/烧录模式串口data信号 | 可配置上拉 |

| PA2/T0CKI/INT | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Timer 0 源头时钟输入,外部中断输入 | 可配置上拉 |

| PA3/MCLRB | 输入 | ST | - | 带电平变化中断的输入,外部复位输入 | 无内部上拉 |

| PA4/CLKO | I/O | - | CMOS | 具有可编程上拉和电平变化中断的I/O,测试时钟输出 | 可配置上拉 |

| PA5 | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O | 可配置上拉 |

| 管脚名 | 功能名 | 输入信号类型 | 输出信号类型 | 具体描述 | 上下拉 |

|---|---|---|---|---|---|

| VDD | 电源 | - | - | 电源正极 | - |

| PA2/T0CKI/INT | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Timer 0 源头时钟输入,外部中断输入 | 可配置上拉 |

| PA1/ICSPDAT | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Debug/烧录模式串口data信号 | 可配置上拉 |

| PA0/ICSPCLK | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O,Debug/烧录模式串口clock信号 | 可配置上拉 |

| PA3/MCLRB | 输入 | ST | - | 带电平变化中断的输入,外部复位输入 | 无内部上拉 |

| PA4/CLKO | I/O | - | CMOS | 具有可编程上拉和电平变化中断的I/O,测试时钟输出 | 可配置上拉 |

| PA5 | I/O | ST | CMOS | 具有可编程上拉和电平变化中断的I/O | 可配置上拉 |

| VSS | 地 | - | - | 电源负极 | - |