在24 V中小功率段,市面主流方案常被“大体积+高BOM”困扰:

用PQ3230,高度>30 mm,塞不进导轨壳;

采用同步整流虽效率高,但成本立刻+3元;

变压器参数各家保密,工程师反复试绕、烫手又烫心。

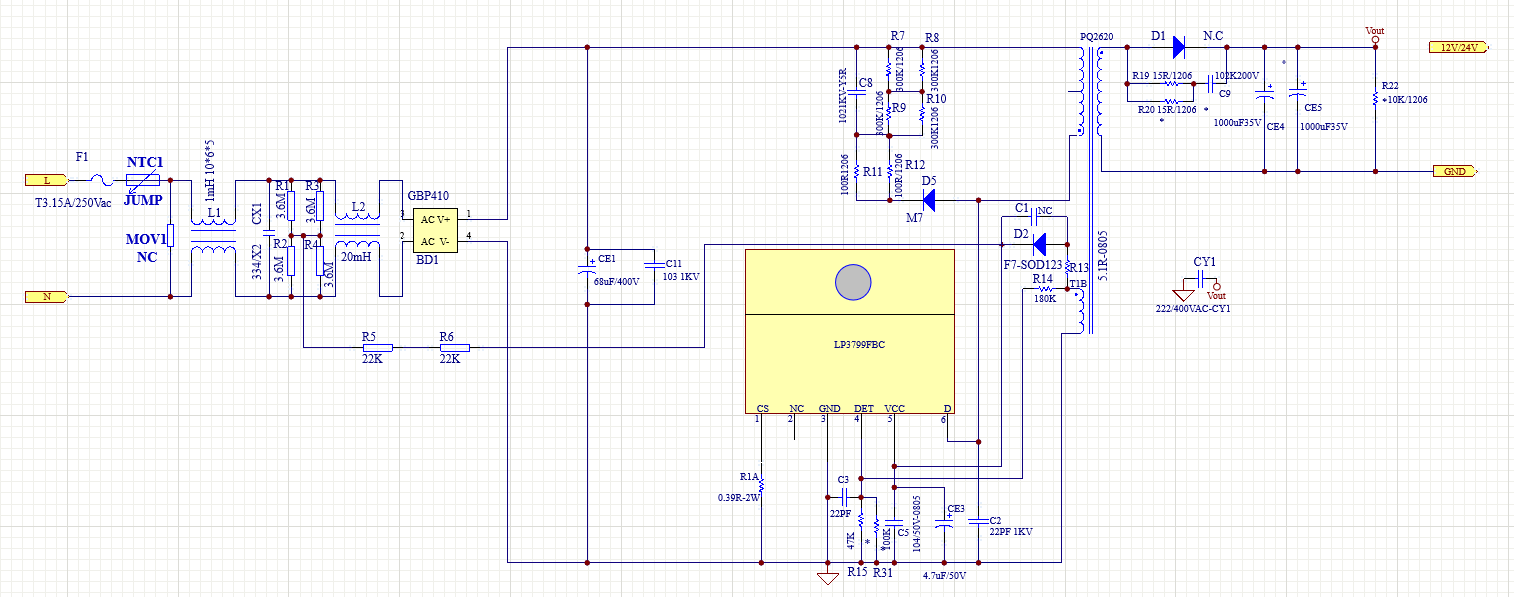

芯茂微LP3799F系列(FAC/FBC仅封装差异,内核同源)给出了一条“PQ2620+二次侧肖特基”的另类路线:

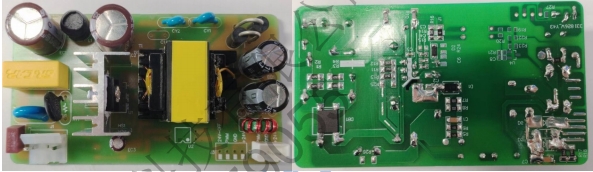

“反激、非连续、谷底导通、125 kHz”四板斧,把24 V×2.5 A=60 W功率硬生生压进PQ2620磁芯,成品尺寸42 mm×28 mm×22 mm,自然冷却,成本<15 RMB(不含壳)。本文把官方只给图片的“非标原理图+变压器手工绕单”一次性公开,并给出可复制的PCB布局、EMI调试与安规要点,供广大电源同行“抄作业”。

内置800 V/2 Ω超结MOS,无需外置散热片即可60 W;

自供电专利,取消辅助绕组,变压器脚位直接省2 Pin;

频率折返+谷底锁定,230 VAC满载效率>88 %,待机<75 mW;

磁芯接地脚位可编程,EMI“热点”自动移位,余量>6 dB;

OTP、OLP、OVP、短路自恢复全打包,过安规IEC/UL62368一步到位。

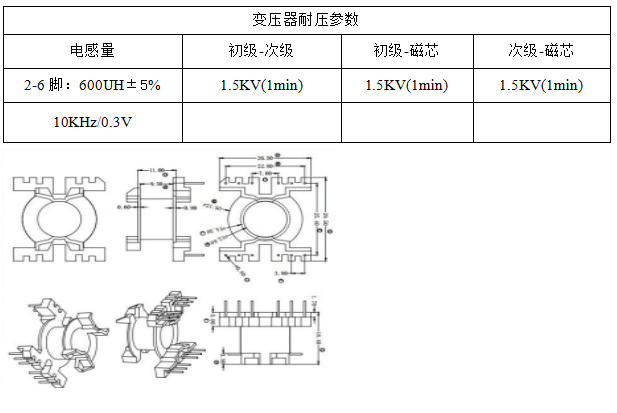

电感量LP 600 µH ±5 %,漏感<30 µH(5 %),气隙0.15 mm(PC40材质,研磨中间柱)

1-NC,2-N1始,3-N1末/N6始,4-N2始,5-N2末/N5始/磁芯接地,6-N6末,8-N3末,12-N3始

→ 注意:5脚为“磁芯+次级公共地”,与PCB铜皮大面积相连,一举解决EMI与ESD

N1:φ0.45 mm×1,36 T,密绕2层,2→3,3层高温胶带

N2:φ0.2 mm×3,7 T,密绕整层,4→5,3层胶带

N3:φ0.65 mm三层绝缘线,10 T,密绕整层,12→8,3层胶带(安规“双重绝缘”)

N5:φ0.2 mm×2,12 T,5→NC,屏蔽层,单端浮空,降低共模

N6:φ0.4 mm×1,14 T,3→6,补偿绕组,辅助芯片自供电(官方取消,但预留更稳)

起绕脚加铁氟龙套管,杜绝“锡尖”刺破胶带

每层胶带≥3层,重叠>50 %,过1.5 kVac耐压

绕完真空含浸,防止音频噪声

成品测试:1 kHz/0.3 V下LP 600 µH ±5 %,漏感<30 µH,Q>60

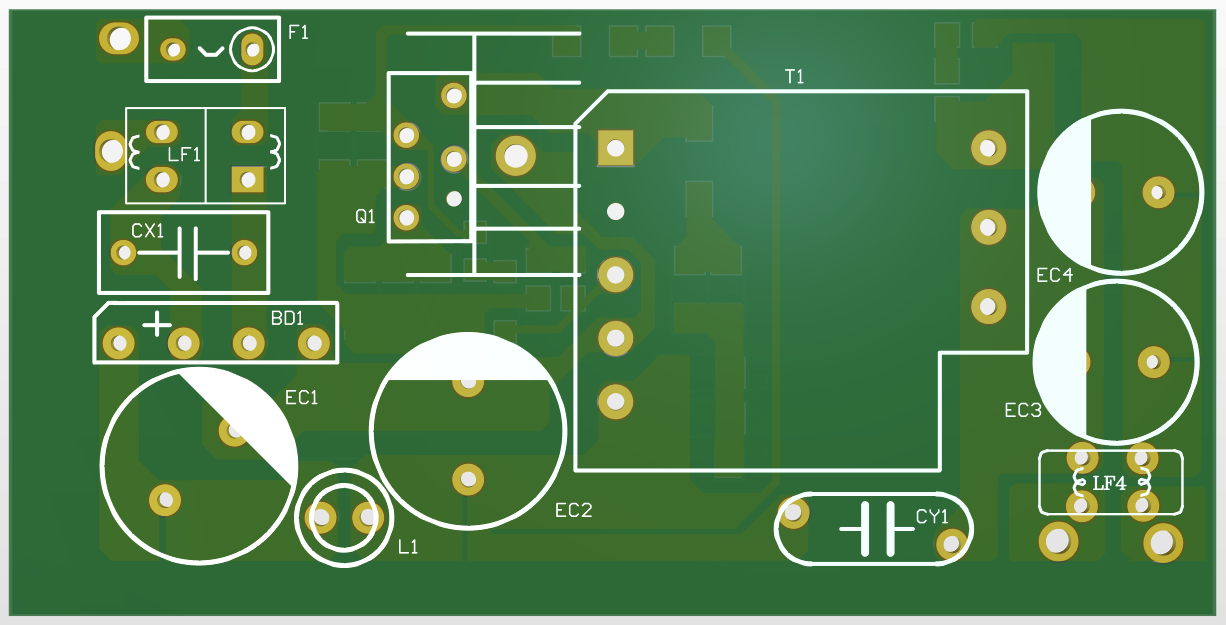

直流母线→变压器→MOS→RCS→母线地,环路面积<1 cm²,差模辐射下降6 dB

芯片GND脚→RCS下地→EC1负→母线地,星型连接,杜绝共阻弹跳

R19/R20分压地单独回芯片GND脚,远离SW节点,误差<±1 %

肖特基阴极→CE4/5→变压器次级地,铜皮上下夹芯,降低ESL

顶层MOS漏极铜箔>200 mm²,反面开窗打散热过孔,60 W温升<45 K

磁芯5脚铜皮预留RC Snubber(100 Ω/1 nF),暗室不过时直接补焊,无需割线

| 负载 | VOUT | IO | Pin | η | Vripple | 壳温 |

|---|---|---|---|---|---|---|

| 100 % | 24.2 V | 2.50 A | 68.2 W | 88.7 % | 120 mV | 65 ℃ |

| 75 % | 24.2 V | 1.88 A | 51.6 W | 88.1 % | 100 mV | 58 ℃ |

| 50 % | 24.2 V | 1.25 A | 35.1 W | 86.3 % | 85 mV | 52 ℃ |

| 25 % | 24.2 V | 0.63 A | 18.9 W | 80.7 % | 70 mV | 45 ℃ |

| 0 % | 24.2 V | 0 A | 0.07 W | — | 40 mV | 35 ℃ |

待机功耗70 mW,满足CoC Tier 2

传导EMI:QP值余量>8 dB@500 kHz,无共模电感即可过Class B

浪涌:±2 kV差模/±4 kV共模,输出无复位

短路:自恢复,打嗝模式,MOS尖峰<650 V(800 V耐压余量23 %)

LP3799FAC/LP3799FBC 这颗“老炮儿”芯片,只要变压器绕得溜,就能从 18W 干到 60W。本文把原理图、PCB、变压器绕制数据、全套实测数据全部开源,欢迎直接打样。