在当今电子设备设计中,工程师常常面临一个挑战:如何在有限的空间和成本内实现功能的多样化和高效性。FT60F210-URT 正是为解决这一问题而生。它以极小的封装(SOT23-6)和高度集成的设计,提供了从存储到外设的全面功能,适用于各种对空间和成本敏感的应用场景。本文将深入解析 FT60F210-URT 的系统框图、管脚定义以及其核心特性,帮助工程师快速掌握其设计要点,提升开发效率。

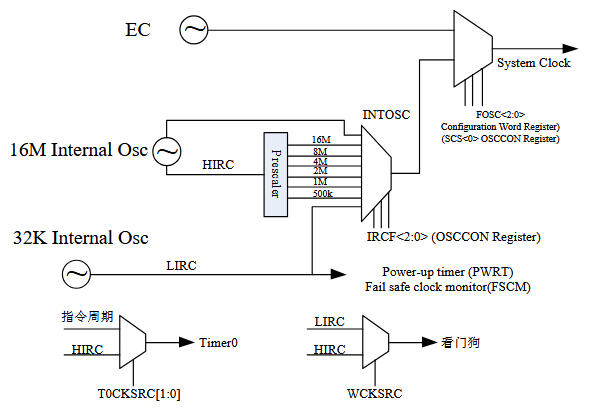

关键信号链:

HIRC/LIRC → 时钟选择器 → CPU/Timer/PWM → GPIO → 外部世界

Touch 模块共享 GPIO,内部 10 nF 基准电容,无需外接。

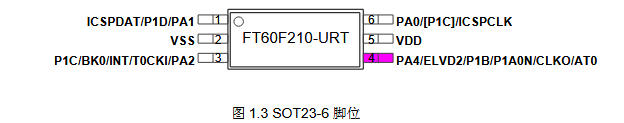

| 管脚 | 名 | 主功能 | 第二/复用 | 说明 |

|---|---|---|---|---|

| 1 | VDD | 2.0-5.5 V 供电 | — | 内置 LVR 2.0/2.2/2.5…4.1 V 可选 |

| 6 | VSS | 地 | — | 星点接地 |

| 2 | PA0 | 数字 IO | ICSPCLK/TK0/P1C | 烧录时钟+触摸通道+PWM |

| 3 | PA1 | 数字 IO | ICSPDAT/TK1/P1D | 烧录数据+触摸+PWM |

| 5 | PA2 | 数字 IO | INT/T0CKI/TK2/P1C | 外部中断/计数器输入/触摸 |

| 4 | PA4 | 数字 IO | CLKO/ELVD1/P1B/P1A0N | 时钟输出/外部LVD/PWM |

设计提示:

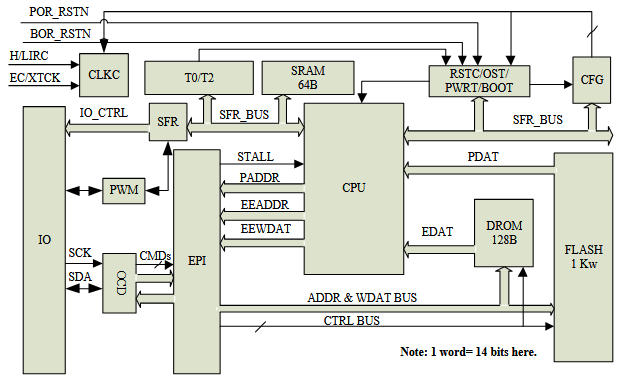

| 项目 | 容量 | 备注 |

|---|---|---|

| Flash | 1K ×14 | 0x000-0x3FF,最后 16 字为中断向量 |

| SRAM | 64 B | 0x20-0x5F,Bank0 |

| EEPROM | 128 B | 独立地址空间,2 ms 自定时写完成 |

| 堆栈 | 8 级硬件 | 不可软件访问,子程序/中断自动压栈 |

| 外设 | 说明 |

|---|---|

| Timer0 | 8 位,共用 8 位预分频,可外部计数 |

| Timer2 | 16 位,PR2 双缓冲,后分频 1-16 |

| PWM1 | 4 路独立 16 位占空比,P1A 带互补死区,最高 256 kHz(16M/64/1024) |

| Touch | 4 通道,自动扫描,阈值可设,中断唤醒 |

| WDT | 16 位,LIRC/HIRC 可选,1-65536 分频 |

| LVD | 1.2-4.0 V 8 档,可测外部电压,作刹车源 |

VDD ──►104──┐

C

│

PA4──LED_R──┤

PA0──LED_G──┤ 共阳 RGB

PA1──LED_B──┘

PA2──按键(触摸或机械)

VSS─────────►GND

FT60F210-URT 把“最小系统”浓缩成一颗 SOT23-6:

FT60F210-URT 以其极小的封装和强大的功能集成,为工程师提供了一种高效、灵活的解决方案。它不仅满足了现代电子设备对低功耗、高集成度和快速开发的需求,还通过减少外围元件数量,显著降低了系统成本和设计复杂性。深圳三佛科技提供样品,技术支持~